## AMIETE - ET (NEW SCHEME) Code: AE74

**Subject: VLSI DESIGN**

**DECEMBER 2010 Time: 3 Hours** Max. Marks: 100

NOTE: There are 9 Questions in all.

- Question 1 is compulsory and carries 20 marks. Answer to Q. 1. must be written in the space provided for it in the answer book supplied and nowhere else.

- The answer sheet for the Q.1 will be collected by the invigilator after half an hour of the commencement of the examination.

- Out of the remaining FICHT Questions ensure any FIVE Questions. Fach question

| Q.1 | Choose the correct or the best alternative in the following:               |                                                                | $(2\times10)$ |

|-----|----------------------------------------------------------------------------|----------------------------------------------------------------|---------------|

|     | a. MOS transistor with implant channel is called as                        |                                                                |               |

|     | (A) bipolar<br>(C) BiCMOS                                                  | <ul><li>(B) enhancement</li><li>(D) depletion</li></ul>        |               |

|     | b. Substrate in nMOS is                                                    |                                                                |               |

|     | <ul><li>(A) N type</li><li>(C) polysilicon</li></ul>                       | (B) P type (D) metal                                           |               |

|     | c. Switching speed of MOS transistor is inversely proportional to channel. |                                                                | of the        |

|     | <ul><li>(A) square of length</li><li>(C) square root of length</li></ul>   | <ul><li>(B) length</li><li>(D) three times of length</li></ul> |               |

|     | d. Zpd/Zpu for an nMOS inverter                                            | ·                                                              |               |

|     | (A) 1/6<br>(C) 1/8                                                         | ( <b>B</b> ) 1/16 ( <b>D</b> ) 1/4                             |               |

|     | e. latch up in CMOS circuit exists in                                      |                                                                |               |

|     | <ul><li>(A) P-well only</li><li>(C) P-well and n-well</li></ul>            | <ul><li>(B) n-well only</li><li>(D) twin tup</li></ul>         |               |

|     | f. Feature size of MOS transistor is                                       |                                                                |               |

|     | (A) $2\lambda \times 2\lambda$                                             | (B) $\lambda \times \lambda$                                   |               |

|     | (C) $4\lambda \times 4\lambda$                                             | ( <b>D</b> ) $\frac{\lambda}{2} \times \frac{\lambda}{2}$      |               |

|     |                                                                                                                               | ( <b>A</b> ) 0.0005 pF<br>( <b>C</b> ) 0.01 pF                                                            | ( <b>B</b> ) 0.04 pF<br>( <b>D</b> ) 0.02 pF |         |  |  |  |

|-----|-------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|----------------------------------------------|---------|--|--|--|

|     | h. Overall delay fd for nMOS cascaded inverter driven by large capacitive load                                                |                                                                                                           |                                              |         |  |  |  |

|     |                                                                                                                               | (A) 3.5 eN τ<br>(C) 1.5 eN τ                                                                              | (B) 4.5 eN τ<br>(D) 2.5 eN τ                 |         |  |  |  |

|     | i. Gate Area Ag is scaled by                                                                                                  |                                                                                                           |                                              |         |  |  |  |

|     |                                                                                                                               | ( <b>A</b> ) 1/α                                                                                          | <b>(B)</b> 1/β                               |         |  |  |  |

|     |                                                                                                                               | (C) $1/\alpha^2$                                                                                          | <b>(D)</b> $1/\beta^2$                       |         |  |  |  |

|     | j. In constant field scaling model                                                                                            |                                                                                                           |                                              |         |  |  |  |

|     |                                                                                                                               | $(\mathbf{A}) \ \alpha = \frac{1}{\beta}$                                                                 | <b>(B)</b> $\beta = 1$                       |         |  |  |  |

|     |                                                                                                                               | (C) $\beta = \alpha$                                                                                      | <b>(D)</b> $\alpha = 1$                      |         |  |  |  |

|     | Answer any FIVE Questions out of EIGHT Questions.  Each question carries 16 marks.                                            |                                                                                                           |                                              |         |  |  |  |

| Q.2 | a.                                                                                                                            | a. With neat diagram explain the working of enhancement mode nMOS transistor. (8)                         |                                              |         |  |  |  |

|     | b.                                                                                                                            | Design the inverter using CMOS lo                                                                         | ogic. Explain its characteristics also.      | (8)     |  |  |  |

| Q.3 | $\mathbf{J}_{\mathbf{d}s}$ a. Derive an expression for $\mathbf{I}_{\mathbf{d}s}$ in non saturated and saturated region. (10) |                                                                                                           |                                              | (10)    |  |  |  |

|     | b. What is body effect? Explain briefly how threshold voltage Vt will be affected by body effect.                             |                                                                                                           |                                              | (6)     |  |  |  |

| Q.4 | a.                                                                                                                            | a. Obtain pull up to pull down ratio for a nMOS inverter driven through one or more pass transistor. (10) |                                              |         |  |  |  |

|     | b.                                                                                                                            | Explain the working of MOSFET.                                                                            |                                              | (6)     |  |  |  |

| Q.5 | a.                                                                                                                            | Write $\lambda$ based design rules for wire                                                               | es and transistor.                           | (8)     |  |  |  |

|     | b.                                                                                                                            | Define sheet resistance and standar                                                                       | d capacitance for a feature size transis     | tor.(8) |  |  |  |

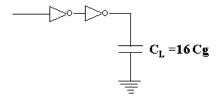

| Q.6 | a. Derive an expression for total delay for N-cascaded inverters driving a large capacitive load. (8)                         |                                                                                                           |                                              | _       |  |  |  |

|     |                                                                                                                               |                                                                                                           |                                              |         |  |  |  |

g. Standard unit capacitance value  $\,C_g\,$  for  $5\,\mu\,m$  MOS transistor is \_\_\_\_\_.

b. Two nMOS inverters are cascaded to drive a capacitive load  $C_L = 16C_g$  as shown in Fig.1. Calculate pair delay in terms of  $\tau$ . (8)

| <u>Inverter 1</u>                           | <u>Inverter 2</u>              |

|---------------------------------------------|--------------------------------|

| $Lpu_1 = 16 \lambda$                        | $Lpu_2 = 2\lambda$             |

| $\overline{W}$ pu <sub>1</sub> =2 $\lambda$ | $\hat{\text{Wpu}}_2=2 \lambda$ |

| $Lpd_1 = 2 \lambda$                         | $Lpd_2 = 2 \lambda$            |

| $Wpd_1=2 \lambda$                           | Wpd <sub>2</sub> =8 $\lambda$  |

Fig. 1

- **Q.7** a. Obtain scaling factor for the following:

- (i) Parasitic capacitance (ii) Channel resistance (iii) Gate delay

- (iv) Saturation current (8)

- b. Design a two-line to four-line decoder circuit to the mask layout level and determine its boundary box. (8)

- Q.8 a. Design two input NOR gate using CMOS. (6)

- b. Write an example of an inverter showing that the power dissipation decreases at the expense of area. (10)

- Q.9 a. Write a note on design styles in VLSI. (6)

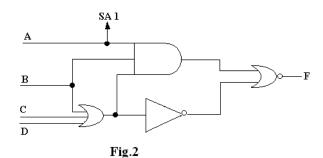

- b. Obtain test-vector for the Fig.2, using sensitised path based testing. (10)