## **DECEMBER 2008**

Code: AE09

**Subject: ANALOG & DIGITAL ELECTRONICS**

Time: 3 Hours Max. Marks: 100

NOTE: There are 9 Questions in all.

- Question 1 is compulsory and carries 20 marks. Answer to Q. 1. must be written in the space provided for it in the answer book supplied and nowhere else.

- Out of the remaining EIGHT Questions answer any FIVE Questions. Each question carries 16 marks.

- Any required data not explicitly given, may be suitably assumed and stated.

## Q.1 Choose the correct or best alternative in the following: (2x10)

- a. A PLA can be used

- (A) as a microprocessor logic.

- (B) a combinational logic.

- **(C)** a sequential logic.

- **(D)** None of above.

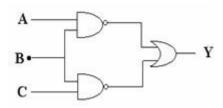

- b. For the logic circuit shown the O/P Y is equal to

- (A)  $\overline{ABC}$ .

- (B)  $\overline{A} + \overline{B} + C$

- (C)  $\overline{A} + \overline{B} + \overline{C}$ .

- (D)  $\overline{AB} + \overline{BC}$ .

- c. Which one is the fastest logic family

- (A) ECL.

(B) TTL.

(C) NMOS.

- (D)  $T^2L$

- d. If each input voltage is amplified by a different factor at the output then the opamp circuit is called as

|    | <ul><li>(A) Averaging amplifier.</li><li>(C) Scaling amplifier.</li></ul>                                                                                                         | <ul><li>(B) Summing amplifier.</li><li>(D) Differential amplifier.</li></ul>        |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| e. | The input resistance of 741 op-amp is                                                                                                                                             |                                                                                     |

|    | (A) $10 \ \mathbf{M}\Omega$ .<br>(C) $100 \ \Omega$ .                                                                                                                             | (B) $1 \text{ M}\Omega$ .<br>(D) $1 \text{ K}\Omega$ .                              |

| f. | The ratio of change in input offset v is called                                                                                                                                   | oltage when variation in supply voltage is made,                                    |

|    | (A) SVRR                                                                                                                                                                          | (B) Slew rate                                                                       |

|    | (C) CMRR                                                                                                                                                                          | (D) Voltage gain                                                                    |

| g. | A 1:16 demultiplexer has following features                                                                                                                                       |                                                                                     |

|    | <ul> <li>(A) 1 I/P, 16 O/P's, 4 control signals.</li> <li>(B) 2 I/P, 8 O/P's, 2 control signals.</li> <li>(C) 2 I/P, 8 O/P's, 2 strobe signals.</li> <li>(D) 16 O/P's.</li> </ul> |                                                                                     |

| h. | nity gain bandwidth Product of 741 op-amp is                                                                                                                                      |                                                                                     |

|    | ( <b>A</b> ) 4 MHz                                                                                                                                                                | <b>(B)</b> 6 MHz                                                                    |

|    | (C) 1 MHz                                                                                                                                                                         | <b>(D)</b> 100 Hz                                                                   |

| i. | A notch filter is a                                                                                                                                                               |                                                                                     |

|    | <ul><li>(A) Wide band pass filter</li><li>(C) Wide band reject filter</li></ul>                                                                                                   | <ul><li>(B) Narrow band pass filter</li><li>(D) Narrow band reject filter</li></ul> |

| j. | The number of flip flop required to construct MOD-7 counter that counts from 0 to s                                                                                               |                                                                                     |

|    | (A) 4.<br>(C) 2.                                                                                                                                                                  | <ul><li>(B) 3.</li><li>(D) 1.</li></ul>                                             |

|    |                                                                                                                                                                                   |                                                                                     |

## Answer any FIVE Questions out of EIGHT Questions. Each question carries 16 marks.

Q.2 a. Explain the factors that determines the operating speed of Logic gate. Discuss, how the speed performance can be improved in Schottky TTL transistors. (8)

and explain **(8)** 0.3 a. Explain the architecture of 741 op-amp? Discuss the operation of each block? **(8)** b. Draw the circuit of a MOS operational amplifier & explain its operation. **(8)** a. Compare and contrast a programmable logic array with a programmable array 0.4 logic (PAL). **(6)** b. Write the acronyms EPROM & E<sup>2</sup>PROM. **(2)** c. What do you mean by priority encoder and explain the priority encoder for 10 line decimal to 4 line BCD with its truth table? **(8)** a. What is race around condition in JK flip flop? How this condition will be Q.5 overcome? **(8)** b. Explain how shift register can be used as (i) serial to parallel data converter, and (ii) parallel to serial data converter. **(8)** 0.6 a. What are the different types of A/D converter? Explain the converter, which is designed to convert analog wave form into binary code. **(8)** b. Explain Dual slope converter. Discuss the advantages & disadvantages of Dual slope converter. **(8) Q.7** a. What types of MOSFET is used in CMOS logic family? Mention its advantages & disadvantages with a neat sketch. Also describe the CMOS NOR gate. (12)b. Draw the circuit symbol for transmission gate? Explain the operation of transmission gate in short. **Q.8** a. Explain how switched capacitor filter behaves as a resistance with a circuit diagram. b. Determine the order of 1-dB ripple Chebyshev filter that gives a 40 dB attenuation at  $\varpi/\varpi c = 2$ . Determine the 3-dB bandwidth of the filter. **(8)** Write short notes on any **TWO** of the following: 0.9 N-MOS logic circuits. (i) (ii) log and antilog amplifiers.

b. Write the various features of ECL family and draw the basic ECL logic NOR gate

- (iii) Digital comparator.(iv) Seven segment display system.(8+8)