2/12/12 Code: A-20

## **AMIETE - ET (OLD SCHEME)**

| Code: AE27           | Subject: DIGITAL HARDWARE DESIGN |                 |

|----------------------|----------------------------------|-----------------|

| <b>Fime: 3 Hours</b> | DECEMBER 2009                    | Max. Marks: 100 |

NOTE: There are 9 Questions in all.

• Question 1 is compulsory and carries 20 marks. Answer to Q.1 must be written in the space provided for it in the answer book supplied and nowhere else.

| Q.1 | Cł | oose t                                                                                                                            | he correct or the bes        | (2x10)                                      |            |  |  |  |

|-----|----|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------|---------------------------------------------|------------|--|--|--|

|     | a. | Т                                                                                                                                 | The outputs of a syste       | resent inputs and previous stored values in |            |  |  |  |

|     |    |                                                                                                                                   |                              |                                             |            |  |  |  |

|     |    |                                                                                                                                   | Combinational system         | 1                                           |            |  |  |  |

|     |    | (B)<br>(C)                                                                                                                        | Sequential system RTL system |                                             |            |  |  |  |

|     |    | (D)                                                                                                                               | None of above                |                                             |            |  |  |  |

|     | b. | Mode                                                                                                                              | eling a digital design as    | a set of components and interconnections    | is done in |  |  |  |

|     |    | (A) D                                                                                                                             | ata flow design              | (B) Behavioural design                      |            |  |  |  |

|     |    |                                                                                                                                   | Tixed style design           | ( <b>D</b> ) Structural design              |            |  |  |  |

|     | c. | c. The Boolean algebra expression $(x + x')y =$                                                                                   |                              |                                             |            |  |  |  |

|     |    | (A) x                                                                                                                             |                              | <b>(B)</b> y                                |            |  |  |  |

|     |    | <b>(C)</b> x                                                                                                                      | +y                           | <b>(D)</b> x'+y                             |            |  |  |  |

|     | d. | In                                                                                                                                | state machine,               | output is a function of and                 | 1          |  |  |  |

|     |    | (A) N                                                                                                                             | Mealy, present-state, ex     | ternal inputs                               |            |  |  |  |

|     |    | <b>(B)</b> N                                                                                                                      | Moore, present-state, ex     | ternal inputs                               |            |  |  |  |

|     |    | ` ′                                                                                                                               | lealy, next-state, extern    | 1                                           |            |  |  |  |

|     |    | <b>(D)</b> N                                                                                                                      | floore, next-state, exter    | nal inputs                                  |            |  |  |  |

|     | e. | A Pro                                                                                                                             | ogrammable Array Log         | c (PAL) has                                 |            |  |  |  |

|     |    | (A) H                                                                                                                             | Hardwired AND array          | and a programmable OR array                 |            |  |  |  |

|     |    | (B) Hardwired OR array and a programmable AND array                                                                               |                              |                                             |            |  |  |  |

|     |    | <ul><li>(C) Programmable AND array and a programmable OR array</li><li>(D) Hardwired AND array and a hardwired OR array</li></ul> |                              |                                             |            |  |  |  |

**(A)** 7

f. What is value of base r if  $(121)_r = (144)_8$ ?

**(B)** 8

**(C)** 9

**(D)** 10

- g. The circuit shown in Fig. 1 detects the following sequence

- **(A)** 0001

**(B)** 0111

**(C)** 0101

**(D)** 1111

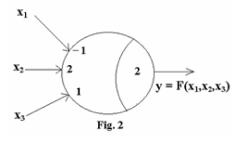

- h. The threshold element shown in Fig.2, realises the switching function, where  $Y = f(x_1, x_2, x_3)$

- (A)  $Y = \Sigma (1,2,3,6,7)$

- **(B)**  $Y = \Sigma (2,3,7)$

- (C)  $Y = \Sigma (1,2,4,5)$

- **(D)**  $Y = \Sigma (2,5,6,7)$

- i. A modulo-P twisted-tail ring counter uses

- (A) P binary variable

- (B) 2P binary variable

- **(C)** P/2 binary variable

- **(D)** None of the above

- j. Typical uses of shifters include

- (A) Removal of the leading (or trailing) bits of a vector

- **(B)** Performing multiplication or division by a power of two.

- (C) Extracting a subvector from a bit-vector

- (D) All the above

## Answer any FIVE Questions out of EIGHT Questions. Each question carries 16 marks.

**Q.2** a. Use the tabulation procedure to generate the set of prime implicants and to obtain *all* minimal expressions for the following function:

$$f(v, w, x, y) = \sum (1,5,6,12,13,14) + \sum_{\Phi} (2,4)$$

(9)

b. Find whether the function

$f(\mathbf{w}, \mathbf{x}, \mathbf{y}, \mathbf{z}) = \sum (0,1,3,5,8,10,11,12,13,15)$  is symmetric and if so express the function in symmetric notation. (7)

Q.3 a. Explain the following:-

2/12/12 Code: A-20

|             |    | <ul><li>(1) FPGAs</li><li>(2) Shift registers</li><li>(3) Priority encoder</li></ul>                                                                                                   | (9)                                                         |  |  |

|-------------|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|--|--|

|             | b. | Using a ROM, implement a system that converts from BCD to Seven segments                                                                                                               |                                                             |  |  |

| Q.4         |    | Implement the following function with NAND gates:-                                                                                                                                     |                                                             |  |  |

| _           |    | $\widehat{f}(x,y,z) = \sum (0,6)$                                                                                                                                                      | (6)                                                         |  |  |

|             | b. | Explain features of Computer Aided Design Tools.                                                                                                                                       | (4)                                                         |  |  |

|             | c. | Explain how functional decomposition is done. Give an example.                                                                                                                         | (6)                                                         |  |  |

| Q.5         | a. | Explain identification and realization of threshold functions.                                                                                                                         | (5)                                                         |  |  |

|             | b. | Give an example of data sub system and control sub system.                                                                                                                             | (7)                                                         |  |  |

|             |    | c. Explain explicit sequencing and microinstruction sequencing.                                                                                                                        | implicit sequencing used in (4)                             |  |  |

| Q.6         | a. | Explain critical race and non-critical race used in asynchronous sequential (5)                                                                                                        | machines.                                                   |  |  |

|             | b. | Explain limitations of finite state machines.                                                                                                                                          | (3)                                                         |  |  |

|             | c. | Draw the ASM chart and state diagram for the synchronous circuit, which has enable input E, clock and outputs A B, C. (8)                                                              |                                                             |  |  |

|             |    | <ul> <li>(i) If E= 1, on every rising edge of the clock code on output A, B, and C chan 111 → 000 and repeats.</li> <li>(ii) If E= 0, then the circuit holds present state.</li> </ul> | $ages from 000 \rightarrow 011 \rightarrow 101 \rightarrow$ |  |  |

| <b>Q.</b> 7 | a. | Write short notes on:  (i) Horizontal and vertical microinstruction format  (ii) Synchronous sequential machine and asynchronous sequential machine                                    | (8)                                                         |  |  |

|             | b. | Draw the structure of microprogrammed controller and explain its functionality.                                                                                                        | (8)                                                         |  |  |

| Q.8         | a. | Write VHDL code for the following:- (8) (i) 3×8 decoder (ii) JK flip flop                                                                                                              |                                                             |  |  |

|             |    | b. Draw the block diagram of Programmable Sequential Array (PSA) and (4)                                                                                                               | explain various inputs and outputs.                         |  |  |

|             | c. | Explain minimization of flow tables in synchronous sequential machines.                                                                                                                | (4)                                                         |  |  |

| Q.9         | a. | Design full subtractor using structural modeling, in VHDL.                                                                                                                             | (6)                                                         |  |  |

|             | b. | Mention various components used in VHDL design.                                                                                                                                        | (4)                                                         |  |  |

2/12/12 Code: A-20

c. Compare behavioural, structural and data flow models used in VHDL. (6)