## AMIETE - ET (OLD SCHEME)

Code: AE09 **Subject: ANALOG & DIGITAL ELECTRONICS Time: 3 Hours** Max. Marks: 100

## **DECEMBER 2010**

NOTE: There are 9 Questions in all.

• Question 1 is compulsory and car:

| <ul><li>in the a hour</li><li>Out o quest</li></ul> | e space provided for it in the ansuser sheet for the Q.1 will be of the commencement of the exf the remaining EIGHT Question carries 16 marks. | swer bo<br>e collec<br>aminat<br>stions a | ted by the invigilator after half an                                               |        |

|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|------------------------------------------------------------------------------------|--------|

| Q.1                                                 | Choose the correct or the bes                                                                                                                  | t altern                                  | ative in the following:                                                            | (2×10) |

| a                                                   | In a differential amplifier, CMRR can be improved by using an increased                                                                        |                                           |                                                                                    |        |

|                                                     | <ul><li>(A) emitter resistance</li><li>(C) source resistance</li></ul>                                                                         | ,                                         | B) collector resistance D) power supply voltage                                    |        |

| b                                                   | b. Ability of an operational amplifier to provide sufficient differential most signal but to reject the common mode signal is given by         |                                           |                                                                                    |        |

|                                                     | <ul><li>(A) Closed loop gain</li><li>(B) Open loop gain</li><li>(C) CMRR.</li><li>(D) none of the above.</li></ul>                             |                                           |                                                                                    |        |

| c                                                   | . A notch filter is a                                                                                                                          |                                           |                                                                                    |        |

|                                                     | <ul><li>(A) Wide band pass filter.</li><li>(C) Wide band reject filter.</li></ul>                                                              |                                           | <ul><li>B) Narrow band pass filter.</li><li>D) Narrow band reject filter</li></ul> |        |

| d                                                   | d. The number of comparators required to build an eight-bit sin flash A/D converter is                                                         |                                           |                                                                                    | or     |

|                                                     | (A) 127<br>(C) 255                                                                                                                             | •                                         | B) 63<br>D) 8                                                                      |        |

| e                                                   | . A data selector is also called a                                                                                                             |                                           |                                                                                    |        |

|                                                     | <ul><li>(A) De-multiplexer</li><li>(C) Multiplexer</li></ul>                                                                                   |                                           | B) Priority encoder D) Decoder                                                     |        |

| f.                                                  | In a 1:16 demultiplexer, the number of control inputs will be                                                                                  |                                           |                                                                                    |        |

|                                                     | (A) 4<br>(C) 2                                                                                                                                 |                                           | <b>B</b> ) 1<br><b>D</b> ) 16                                                      |        |

| AE09 / D                                            | DEC2010                                                                                                                                        | 1                                         | AMIETE - ET (OLD SCHEME                                                            | Ξ)     |

- g. Identify the slowest of the family listed below

- (A) LSTTL

(B) TTL

(C) ECL

- (D) Low Power TTL

- h. The number of flip-flops needed to construct a BCD decade counter is

- **(A)** 4

**(B)** 3

**(C)** 10

- (D) none of these

- i. Size of ROM required to implement a 16:1 multiplexer would be

- (A) 512k\*2

**(B)** 1M\*1

**(C)** 1M\*2

- **(D)** 128\*6

- j. A dynamic RAM consist of

- (A) 6 transistors.

- **(B)** 2 transistors and 2 capacitors

- **(C)** 1 transistors and 1 capacitors.

- **(D)** 2 capacitors only

## Answer any FIVE Questions out of EIGHT Questions. Each question carries 16 marks.

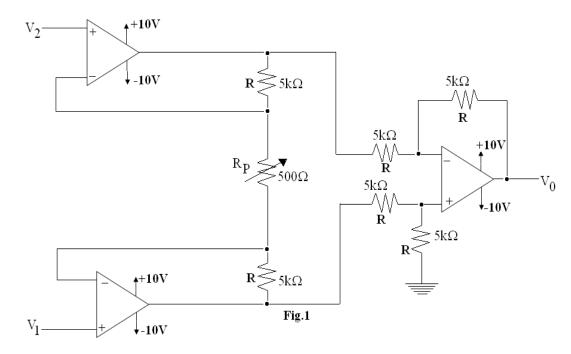

**Q.2** a. Calculate the output voltage in terms of  $V_1$  and  $V_2$  as shown in Fig.1. (8)

b. Define offset voltage and slew rate of an op-amp.

- **(4)**

- c. In context to frequency compensation, explain internal compensation & external compensation. (4)

2

| Q.3 | a. | Determine the order and 3 dB bandwidth of 1 dB ripple Chebyshev filte that gives a 40 dB attenuation at $\omega/\omega_c=2$ .                                                                                                                                                                   | r<br>(8)          |

|-----|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

|     | b. | What are Switched-capacitor filters? List the advantages of switched capacitor filters.                                                                                                                                                                                                         | (8)               |

| Q.4 | a. | The data sheet of a certain eight-bit A/D converter which have the following specifications:  (i) resolution: eight bits  (ii) full-scale error:0.02% of full scale,  (iii) full scale analogue input:+5V.  Determine the quantization error (in volts) and the total possible error (in volts) |                   |

|     | b. | List the applications of Schmitt trigger circuit.                                                                                                                                                                                                                                               | <b>(4)</b>        |

|     | c. | What is Schottky diode? Why it is also called hot-carrier diode? How does in construction from a normal p-n junction diode?                                                                                                                                                                     | it differ (4)     |

| Q.5 | a. | Design a two-input NOR and two-input NAND using NMOS logic.                                                                                                                                                                                                                                     | (8)               |

|     | b. | Explain the working of BJT as an Inverter.                                                                                                                                                                                                                                                      | (8)               |

| Q.6 | a. | Explain the working of CMOS as an inverter.                                                                                                                                                                                                                                                     | (8)               |

|     | b. | Give general properties of the FETs.                                                                                                                                                                                                                                                            | <b>(4)</b>        |

|     | c. | What is the function of buried layer in the fabrication of Bipolar transistors                                                                                                                                                                                                                  | ? (4)             |

| Q.7 | a. | How we interface the TTL-to-ECL family?                                                                                                                                                                                                                                                         | (4)               |

|     | b. | Give the applications of ROM memory.                                                                                                                                                                                                                                                            | (4)               |

|     | c. | Design a 16:1 multiplexer using two 8:1 multiplexer having an active-low ENABLE input.                                                                                                                                                                                                          | v<br>( <b>8</b> ) |

| Q.8 | a. | Design a MOD-10 Johnson counter and also write the count sequence fo the same.                                                                                                                                                                                                                  | r<br>(8)          |

|     | b. | What is the race-around condition and how it can be eliminated?                                                                                                                                                                                                                                 | (8)               |

| Q.9 | a. | Describe the serpentine and LARAM organization of a CCD memory.                                                                                                                                                                                                                                 | (8)               |

|     | b. | A combinational circuit is defined by the functions. $F_1(A,B,C) = \sum m(3,5,7)$ $F_2(A,B,C) = \sum m(4,5,7)$                                                                                                                                                                                  |                   |

|     |    | Implement the circuit with a PLA having 3 inputs, 3 product terms and 2 outputs.                                                                                                                                                                                                                | (8)               |