## **ALCCS**

**AUGUST 2009** Code: CS12

**Subject: COMPUTER ARCHITECTURE Time: 3 Hours** Max. Marks: 100

## **NOTE:**

- Question 1 is compulsory and carries 28 marks. Answer any FOUR questions from the rest. Marks are indicated against each question.

- Parts of a question should be answered at the same place.

- **Q.1** a. Show the hardware implementation of a logic circuit that uses logic gates and generates AND, OR, XOR, complement micro-operations (one signal at a time). The selection is to be based on two input binary signals.

- b. Give the steps involved in memory read operation.

- c. Explain with example a two address instruction format.

- d. How DRAM refresh is implemented?

- e. Where is cache located in computer? What is cache hit & cache miss?

- f. What is write back policy?

- g. What do you understand by "Polling" in I/O subsystem design? **(7** 4)

- **Q.2** a. What is interrupt? Describe different types of interrupts and their use. How a handles non-vectored interrupt? processor a

- b. With neat block diagram explain source initiated and destination initiated hand shaking method for data transfer. State its disadvantages, (10+8)any.

- Q.3 a. Explain the Restoring algorithm for division with a neat flow chart.

- b. Show the register contents at each stage of multiplying by using with Booth's algorithm. (10+8)

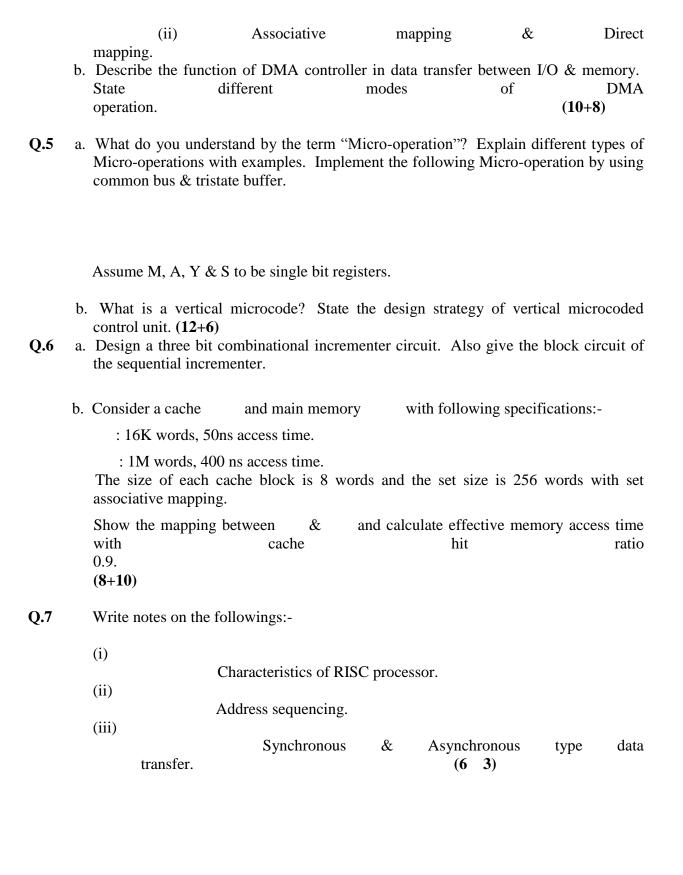

- 0.4 a. Differentiate between

- (i) Isolated and Memory mapped I/O.